Pour construire une station home-made, la première pierre de l'édifice est naturellement le VFO, j'ai de nouveau choisi l'AD9850 cette fois piloté par un PIC.

La fréquence de sortie est réglée par un mot binaire appliqué sur le module DDS soit en parallèle sur ses broches D0 à D7, soit en série sur la broche Data ou la broche D7 (qui sont reliées). La valeur de ce mot binaire est défini par la

formule MotBinaire= (Fq * 2^32)/125, mon module étant cadencé à 125Mhz. Plutôt que de faire effectuer au microcontrôleur des calculs longs et fastidieux à mettre en oeuvre (en assembleur) on peut précalculer certains éléments de la formule:

2^32/125000 = 34359.738, qu'on peut arrondir 34360 sans problème.

De cette façon on allège la programmation et le temps de calcul du micro en faisant MotBinaire = 7012 * 34359.738 = 240930482.856, en assembleur on ne garde que la partie entière 240930482 qui donne en hexa 0x0E5C4EB2, mot à appliquer sur D0 à

D7 et qui nous donnera une belle sinusoïde à 7012Khz. Ce ne sont là que des clés pour ceux qui voudraient s'amuser à programmer un AD9850, pour ma part j'ai choisi une autre façon de faire, comme je n'émet la plupart du temps que sur quelques QRG

choisies sur 80 ou 40m ou je retrouve les copains de CW ces fréquences sont programmées en dur dans le microcontrôleur et la variation se fera autour en jouant sur l'encodeur. A noter qu'on peut toujours parcourir toute la gamme de fréquences

produite par l'AD9850 mais il faut être patient ;D.

Exemple pour 7012Khz:

(7.012 * 2^32)/125 = 240930485

24093048 vaut en hexa: 0x000E5C4EB5 sur 5 octets.

Nota: toujours mettre l'octet de poids fort à 0x00, il est réservé pour les tests d'usine, le modifier risquerait de bloquer le DDS.

----------------------------------------------------------------------------------- Version avec chargement parallèle -----------------------------------------------------------------------------------

On peut programmer l'AD9850 de deux façons, en mode parallèle ou en mode série.

J'ai commencé par la façon la plus facile à mettre en oeuvre coté programmation, le mode parallèle. Pour cela il suffit d'envoyer les 5 octets du mot binaire un par un sur les pins D0 à D7 du DDS en faisant suivre chaque octet par un pulse sur w_clk. Une fois ces 5 octets chargés on valide le tout

par un pulse sur fq_ud. Simple.

Petit exemple avec la fréquence 7012Khz calculée plus haut (0x000ec54eb5):

envoi 0x00, pulse horloge sur w_clk

envoi 0x0E, pulse horloge sur w_clk

envoi 0xC5, pulse horloge sur w_clk

envoi 0x4E, pulse horloge sur w_clk

envoi 0xB5, pulse horloge sur w_clk

validation fréquence par pulse sur fq_ud.

Ceci effectué la sinusoïde doit être présente sur les deux pins out1 et out2.

J'ai éprouvé quelques difficultés à mettre la chose au point sur ma platine de développement à cause de tous les straps de liaisons entre la platine et la breadboard qui forment un véritable chevelu, et qui à partir de 5Mhz se comportaient en antennes

et créaient des accrochages, les joies de la HF. En prenant quelques précautions çà à fini par fonctionner correctement.

Ci-dessous version du code simple avec fréquence fixe pour la compréhension, à noter que le programme boucle indéfiniment pour une raison de lisibilité mais qu'une seule itération suffit pour programmer la fréquence.

Code exemple pour un PIC 18F4525

---=oO(#)0o=---

Ci-dessous VFO fonctionnel commandé par encodeur rotatif, la fréquence est affichée sur un petit fréquencemètre chinois à 8.

Programmation un peu plus complexe que l'exemple ci-dessus mais élaboration du circuit imprimé simplifiée car moins de pistes, le chargement se fait cette fois par un défilement des 40 bits composants les 5 octets, chaque bit étant séparé par un pulse d'horloge w_clk. Une fois les 40 bits chargés un pulse fq_ud vient

valider le tout. Important : pour chaque octet les bits sont chargés dans le sens bit de poids faible à bit de poids fort.

Pour reprendre l'exemple 7012Khz, pour mémoire 0x00=b'00000000', 0x0E=b'00001110', 0x5C= b' 01011100', 0x4E=b'01001110', 0xB5=b'10110101'

Le chargement se fera cette fois de cette manière: (0xb5)10101101, pulse w_clk, (0x4e) 01110010, pulse w_clk, (0x5c) 00111010, pulse w_clk, (0xOe) 01110000, pulse w_clk,

Petite vidéo du vfo dds avec encodeur et chargement série en test sur ma platine d'expérimentation PICplatine V4_28.. On peut entendre la porteuse sur mon récepteur de trafic câlé sur 7012Khz, l'imprécision de l'affichage vient du fréquencemètre chinois, la fréquence issue du DDS est juste avec celui du labo.

# MCBDLS #

-------------------------------------------------------------------------------------------- Version finale avec PCB --------------------------------------------------------------------------------------------

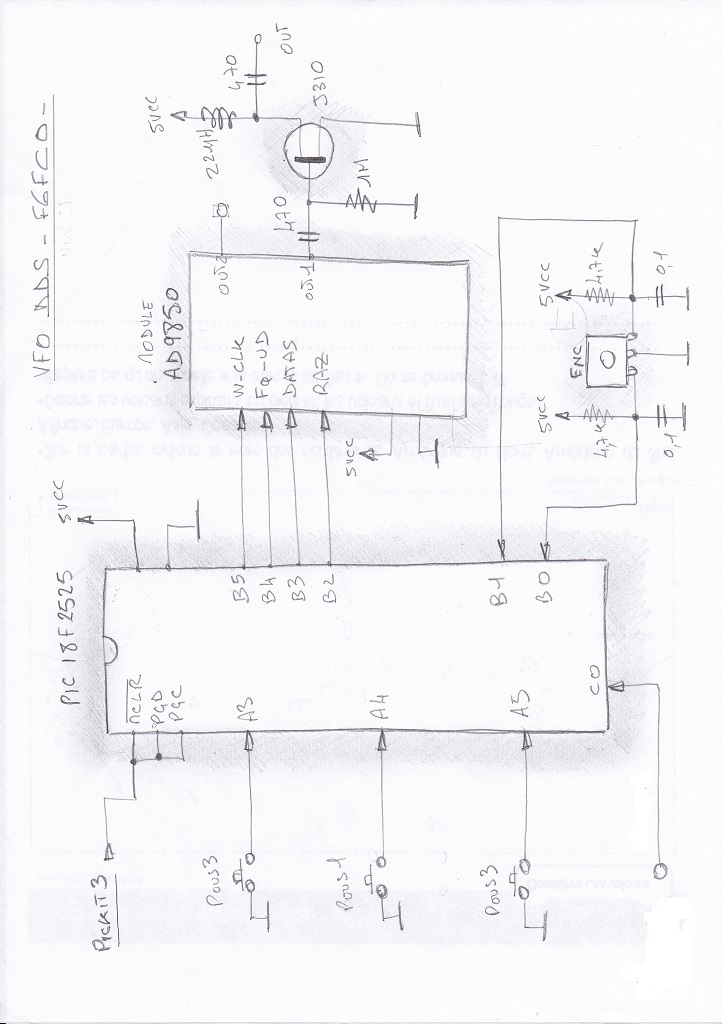

Schéma de principe de la plaquette finale, pour faire plus lisible certains composants telles les pull-up n'y figurent pas, j'ai rajouté des entrées poussoirs pour de probables fonctions futures, on n'est jamais trop prévoyant, à câbler si nécessaire. En sortie un petit préampli HF à FET booste le signal à 1.3v cc. Une entrée pour le Pickit3 est prévue pour pouvoir intervenir directement sur la carte en cas de modifications ultérieures.

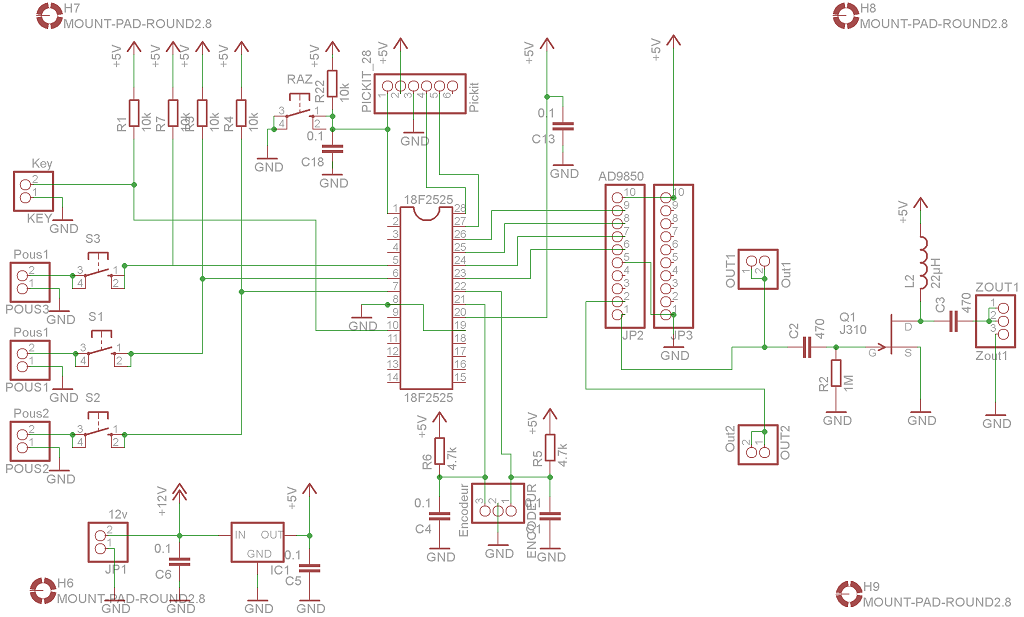

Schéma Eagle définitif et complet.

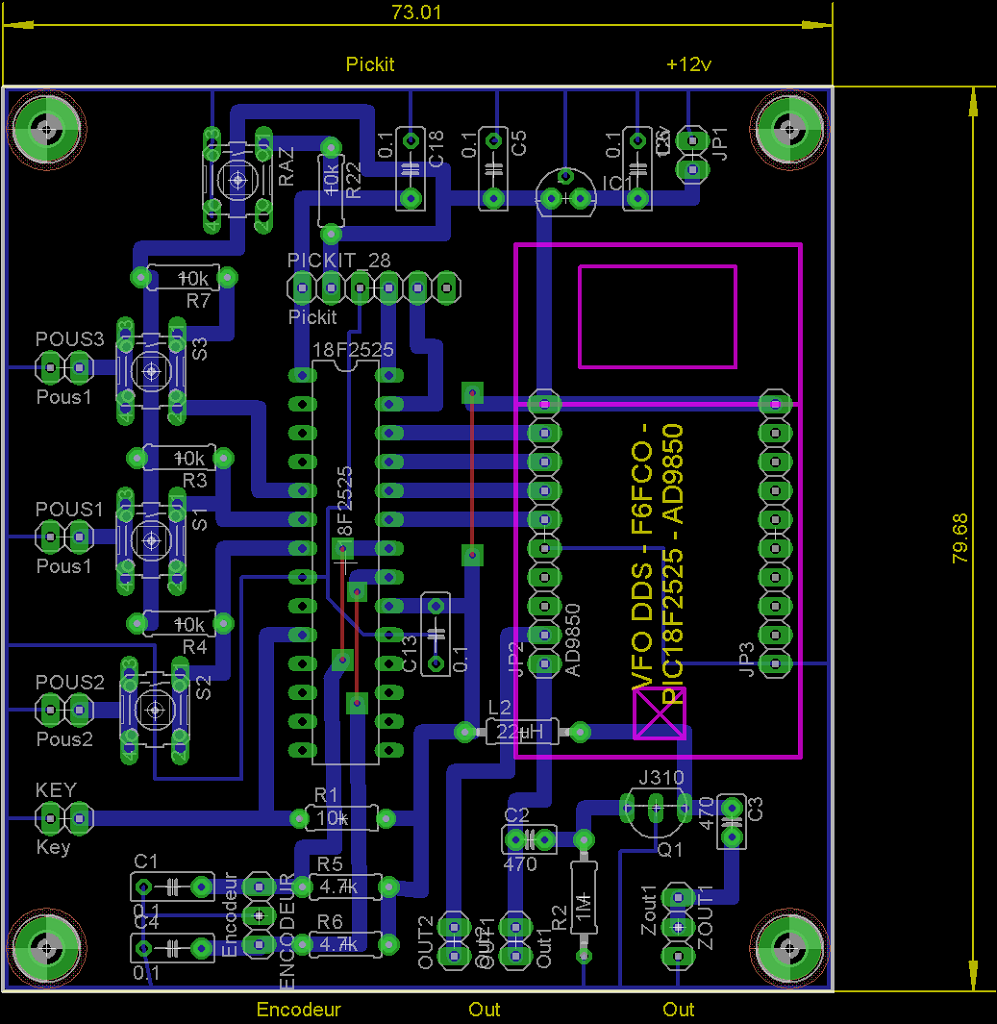

Au final le tout tient sur une plaquette de 73x80mm.

J'aurai pu encore minimiser la plaquette en utilisant des composants CMS mais je préfère les bons vieux PDIP, avec l'avantage non négligeable en prototypage de pouvoir les mettre sur support. Les poussoirs pourront être changés pour de vrais poussoirs de face-avant.

Code hexa pour PIC18F2525 du VFO terminé avec changement de bande par appui poussoir.